NPU vs GPU for Deep Learning Workloads: Navigating the New Era of AI Silicon

NPU vs GPU for Deep Learning Workloads: Navigating the New Era of AI Silicon

AI & Semiconductor Industry Analyst | 8+ Years Covering Emerging Tech

The Great Decoupling: Understanding the AI Hardware Landscape

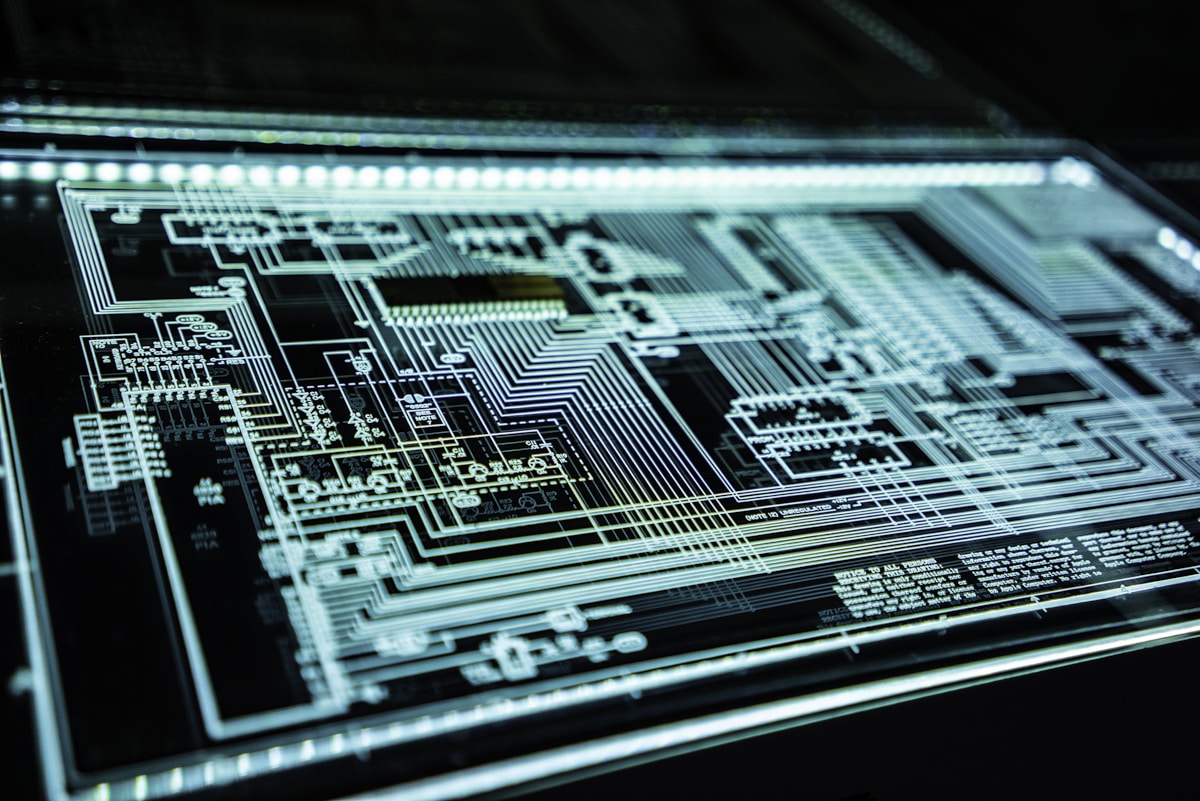

For the past decade, the Graphics Processing Unit (GPU) has served as the primary hardware for artificial intelligence development. Originally engineered for parallel pixel rendering, the GPU’s architecture is well-suited for the matrix multiplications required by neural networks. As the scale of models has increased to trillions of parameters, the industry has seen the rise of the Neural Processing Unit (NPU), a specialized accelerator designed specifically for AI workloads.

Evaluating NPU vs GPU for deep learning workloads is now a requirement for data center architects, mobile device manufacturers, and cloud service providers. Understanding the evolution of semiconductor architectures is essential to identifying why specialized silicon is becoming a standard in high-performance computing.

The GPU: The Versatile Workhorse of Deep Learning

The GPU’s prominence in deep learning is a result of its architectural flexibility. Modern data center GPUs, such as the NVIDIA H100 or the AMD Instinct MI300, feature thousands of cores designed for high-throughput parallel processing. This architecture is highly effective for training—the phase where models process vast datasets to identify patterns.

A primary advantage of the GPU is its established software ecosystem. Frameworks like NVIDIA’s CUDA have provided a stable environment for developers for over 15 years, allowing for the implementation of diverse neural network architectures. Because deep learning research evolves rapidly, the programmable nature of the GPU ensures support for new layer types or activation functions via software updates.

However, this versatility impacts power efficiency and silicon utilization. While data center GPUs are increasingly streamlined for compute, their general-purpose heritage requires significant power. In the context of NPU vs GPU for deep learning workloads, flagship data center GPUs are noted for high Thermal Design Power (TDP), which can reach 700W per chip.

The NPU: Precision-Engineered for Neural Networks

The Neural Processing Unit (NPU)—also known as an AI Accelerator or Tensor Processing Unit (TPU)—is an Application-Specific Integrated Circuit (ASIC). It is designed to accelerate the specific mathematical operations fundamental to neural networks, such as dot products and matrix-vector multiplications.

NPUs optimize performance by reducing the overhead associated with general-purpose processing. Many utilize data-flow architectures where data moves directly between processing elements, reducing the frequency of external memory access. This design improves energy efficiency, often delivering higher Tera-Operations Per Second per Watt (TOPS/Watt) compared to general-purpose hardware.

In edge devices, such as smartphones and laptops utilizing Apple’s M-series Neural Engine or Qualcomm’s Hexagon NPU, the NPU handles persistent AI tasks like computational photography or on-device language processing. Offloading these tasks to the NPU reduces battery consumption and thermal load, allowing the GPU to remain available for graphical tasks.

Architectural Comparison: Latency vs. Throughput

When comparing NPU vs GPU for deep learning workloads, the distinction between throughput and latency is a key technical factor. GPUs are optimized for high throughput, processing massive batches of data simultaneously, which is necessary for the training phase of deep learning.

In contrast, many NPUs are optimized for low-latency inference. Inference is the process of using a trained model to generate a prediction or response from a single input. In real-time applications, such as autonomous navigation or voice recognition, minimizing the time for a single data point to pass through the network is critical. NPUs are architected to reduce this latency, making them effective for real-time AI deployment.

Deployment Scenarios in the Enterprise

The application of these technologies is demonstrated in several industry use cases:

1. Large Language Model (LLM) Training: Training foundation models requires high-precision arithmetic and the flexibility to adapt to evolving Transformer architectures. Currently, GPUs are the standard for this phase due to their robust software stacks and high-precision capabilities.

2. Automotive Edge AI: Autonomous vehicle systems must process sensor data with deterministic low latency to ensure safety. NPUs, such as those found in specialized automotive chips, provide the required processing speed within the strict power and thermal constraints of a vehicle.

3. Mobile Computing: Modern mobile devices use NPUs to manage 'always-on' features and computational photography. This specialization prevents the high battery drain and thermal throttling that would occur if these tasks were managed solely by the GPU.

The Shift Toward Heterogeneous Computing

The current trend in AI hardware is toward heterogeneous computing rather than the total replacement of one architecture by another. Modern Systems-on-Chip (SoCs) integrate CPUs, GPUs, and NPUs, using software schedulers to assign tasks to the most efficient component.

In data centers, this is reflected in hybrid clusters where GPUs manage model training, while specialized NPUs—such as AWS Inferentia or Google TPUs—handle large-scale inference requests. This approach balances the need for developmental flexibility with operational cost efficiency.

Conclusion: Selecting the Appropriate Architecture

The choice of NPU vs GPU for deep learning workloads depends on the specific stage of the AI lifecycle. The GPU remains the standard for model training and research due to its flexibility and software maturity. For enterprises deploying AI at scale, particularly for inference in the cloud or at the edge, the NPU provides a specialized solution for high-performance, energy-efficient processing.

Sources

- NVIDIA Technical Documentation: 'Hopper Architecture'

- Google Cloud: 'TPU Infrastructure Overview'

- IEEE Spectrum: 'Domain-Specific Hardware Trends'

- Apple Technical Specifications: 'M-Series Neural Engine Architecture'

- Gartner: 'Strategic Semiconductor Technology Trends'

This article was AI-assisted and reviewed for factual integrity.

Photo by Unsplash on Unsplash

Post a Comment