Comprehensive Guide to ASIC Design Flow Stages: Navigating the Path from Concept to Silicon

Comprehensive Guide to ASIC Design Flow Stages: Navigating the Path from Concept to Silicon

Senior Technology Analyst | Covering Enterprise IT, AI & Emerging Trends

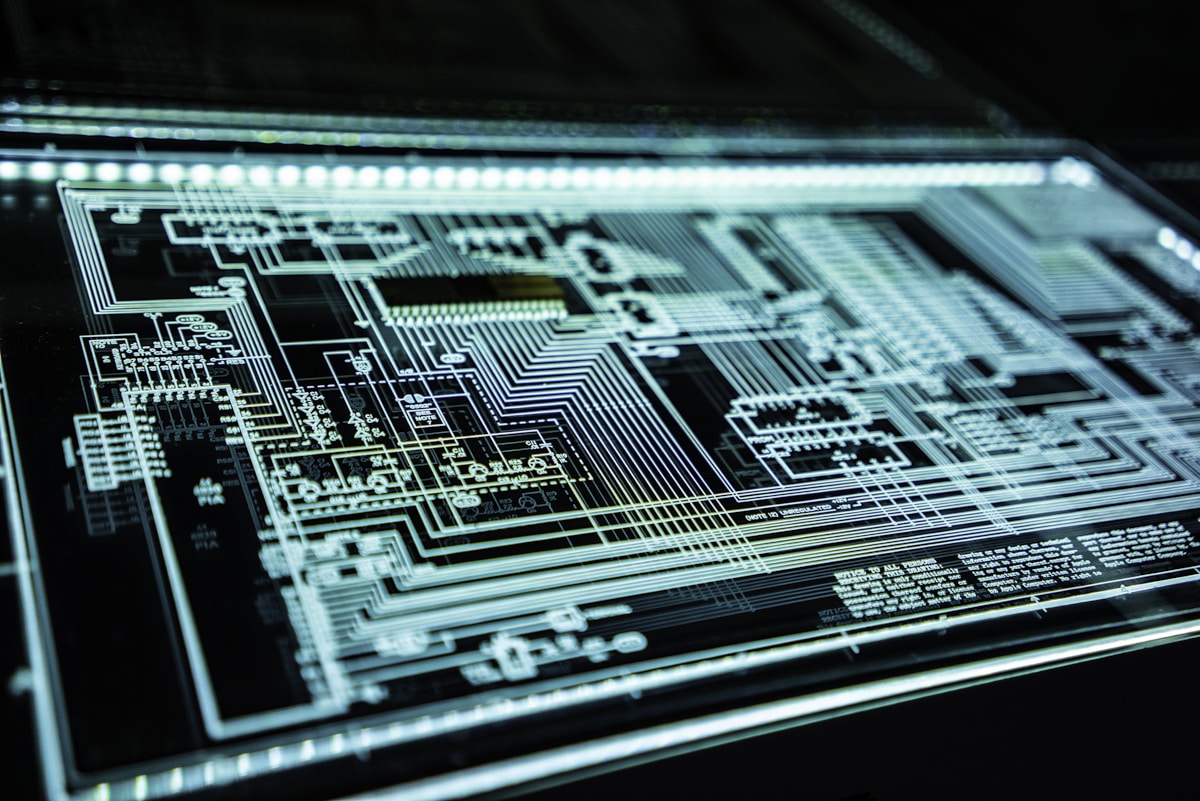

Introduction to Modern ASIC Design

In the current era of hyperscale computing and artificial intelligence, the Application-Specific Integrated Circuit (ASIC) represents the pinnacle of hardware optimization. Unlike general-purpose processors, ASICs are tailored for specific tasks—ranging from cryptographic hashing in blockchain to tensor processing in machine learning. As the industry moves toward sub-5nm process nodes, the complexity of the ASIC design flow has escalated, requiring a seamless integration of logic design, physical implementation, and manufacturing constraints. This guide provides an authoritative breakdown of the essential ASIC design flow stages, contextualized within the broader landscape of Next-Generation Semiconductor Architecture and Advanced Manufacturing.

Stage 1: Design Specification and Architecture Definition

The process begins with a rigorous specification phase. Engineers define the functional requirements, performance targets (throughput, latency), power budgets, and physical dimensions. For example, a designer working on an automotive ADAS (Advanced Driver Assistance System) chip must prioritize low latency and high reliability under extreme thermal conditions. During this stage, architectural decisions are made regarding bus structures (e.g., AMBA AXI), memory hierarchy, and the integration of third-party Intellectual Property (IP) cores. This stage sets the blueprint for the entire project, and errors here can lead to multi-million dollar 're-spins' later in the cycle.

Stage 2: RTL Design and Functional Verification

Once the architecture is frozen, designers write the Register Transfer Level (RTL) code using Hardware Description Languages (HDL) such as Verilog, SystemVerilog, or VHDL. This code describes how data flows between registers and how it is transformed by combinational logic. Verification is the most time-consuming part of the flow, often consuming over 60% of the total design cycle. Using the Universal Verification Methodology (UVM), engineers create complex testbenches to simulate the RTL against the original specification. Realistic examples include running extensive random stimulus through a networking switch design to ensure no packet loss occurs under congested traffic scenarios.

Stage 3: Logic Synthesis

Logic synthesis is the bridge between the abstract RTL code and a physical realization. Using Electronic Design Automation (EDA) tools from industry-standard vendors, the RTL is mapped to a specific Standard Cell Library provided by a foundry. The output is a gate-level netlist. During synthesis, the tool optimizes the design for 'PPA'—Power, Performance, and Area. For instance, if a mobile processor design is exceeding its power envelope, the synthesis tool may swap high-performance, high-leakage transistors for slower, low-leakage alternatives in non-critical paths.

Stage 4: Design for Test (DFT) Insertion

In advanced manufacturing, physical defects are an inevitability. DFT insertion involves adding extra logic to the chip specifically for post-manufacturing testing. Techniques include Scan Chain insertion, Built-In Self-Test (BIST) for memory blocks, and Boundary Scan (JTAG). This ensures that once the silicon returns from the foundry, the manufacturer can quickly identify which chips are functional and which contain defects, thereby protecting the yield and reducing costs for the end customer.

Stage 5: Floorplanning and Partitioning

Floorplanning is the first step of the physical design (back-end) flow. It involves defining the size of the chip die and placing the major functional blocks, I/O pads, and macro cells (like SRAM). A well-executed floorplan minimizes wire length and congestion. For a modern AI accelerator, floorplanning is critical because the massive data movement between the compute engine and HBM (High Bandwidth Memory) requires strategic placement to avoid thermal hotspots and signal degradation.

Stage 6: Placement and Clock Tree Synthesis (CTS)

Following floorplanning, individual standard cells are placed within the rows defined in the floorplan. Once placement is finalized, the design enters Clock Tree Synthesis. The 'clock' is the heartbeat of the ASIC; it must reach every flip-flop on the chip with minimal timing variation. CTS involves building a distribution network of buffers and inverters to minimize 'clock skew' and 'latency.' In high-speed designs operating at high clock frequencies, even a few picoseconds of skew can lead to functional failure.

Stage 7: Routing and Physical Optimization

Routing is the process of creating the physical wires (metal layers) that connect the placed cells. This is performed in two steps: Global Routing and Detail Routing. Modern EDA tools use sophisticated algorithms to navigate through dozens of metal layers while adhering to complex Design Rule Manuals (DRM). During this stage, 'Signal Integrity' (SI) becomes a major concern. As wires get closer together in advanced nodes, crosstalk—where the signal on one wire interferes with another—can cause timing violations or logic errors.

Stage 8: Physical Verification and Sign-off

Before the design is sent to the foundry, it must pass a battery of 'Sign-off' checks. These include Design Rule Checks (DRC) to ensure the layout is manufacturable, Layout vs. Schematic (LVS) to ensure the physical wires match the logical netlist, and Static Timing Analysis (STA) to guarantee the chip will run at the target frequency across all voltage and temperature corners. This is the 'Golden' verification step. For a chip using FinFET or GAA (Gate-All-Around) transistors, these checks are incredibly dense, often requiring massive distributed computing clusters to complete.

Stage 9: Tape-out and GDSII Generation

The final stage is 'Tape-out,' where the completed design is exported as a GDSII or OASIS file. This file contains the geometrical shapes representing every layer of the chip. This data is sent to the semiconductor foundry, where it is used to create the photomasks for the lithography process. This marks the transition from the digital design realm into the physical manufacturing realm, where the principles of Next-Generation Semiconductor Architecture and Advanced Manufacturing are applied to produce the physical silicon wafers.

The Impact of Advanced Packaging

The traditional ASIC flow is currently evolving to include 2.5D and 3D packaging. Instead of a single monolithic die, designers are increasingly using 'chiplets.' This requires an additional stage in the flow: Package-Die Co-design. In this scenario, multiple smaller dies are integrated onto a silicon interposer. This approach circumvents the reticle limit and allows for mixing different process nodes, which is a hallmark of modern semiconductor innovation.

Conclusion

The ASIC design flow is a masterpiece of engineering, transforming a high-level concept into billions of precisely placed transistors. As we push toward the limits of Moore’s Law, each stage—from RTL verification to physical sign-off—becomes more interdependent. Mastery of these stages is a strategic necessity for companies aiming to lead in the fields of AI, telecommunications, and high-performance computing. The future of silicon lies in the refinement of these processes to accommodate the complexities of 3D integration and new materials.

Sources

- IEEE Solid-State Circuits Society: "Trends in Digital Integrated Circuit Design."

- Cadence Design Systems: "The Evolution of the Digital Implementation Flow."

- Synopsys: "Comprehensive Static Timing Analysis and Sign-off."

- TSMC: "Advanced Technology Reference Flows."

This article was AI-assisted and reviewed for factual integrity.

Photo by Unsplash on Unsplash

Post a Comment