Demystifying the RTL to GDSII Design Flow Steps: A Comprehensive Guide to Modern ASIC Implementation

Demystifying the RTL to GDSII Design Flow Steps: A Comprehensive Guide to Modern ASIC Implementation

Senior Technology Analyst | Covering Enterprise IT, AI & Emerging Trends

Introduction to the Digital Implementation Journey

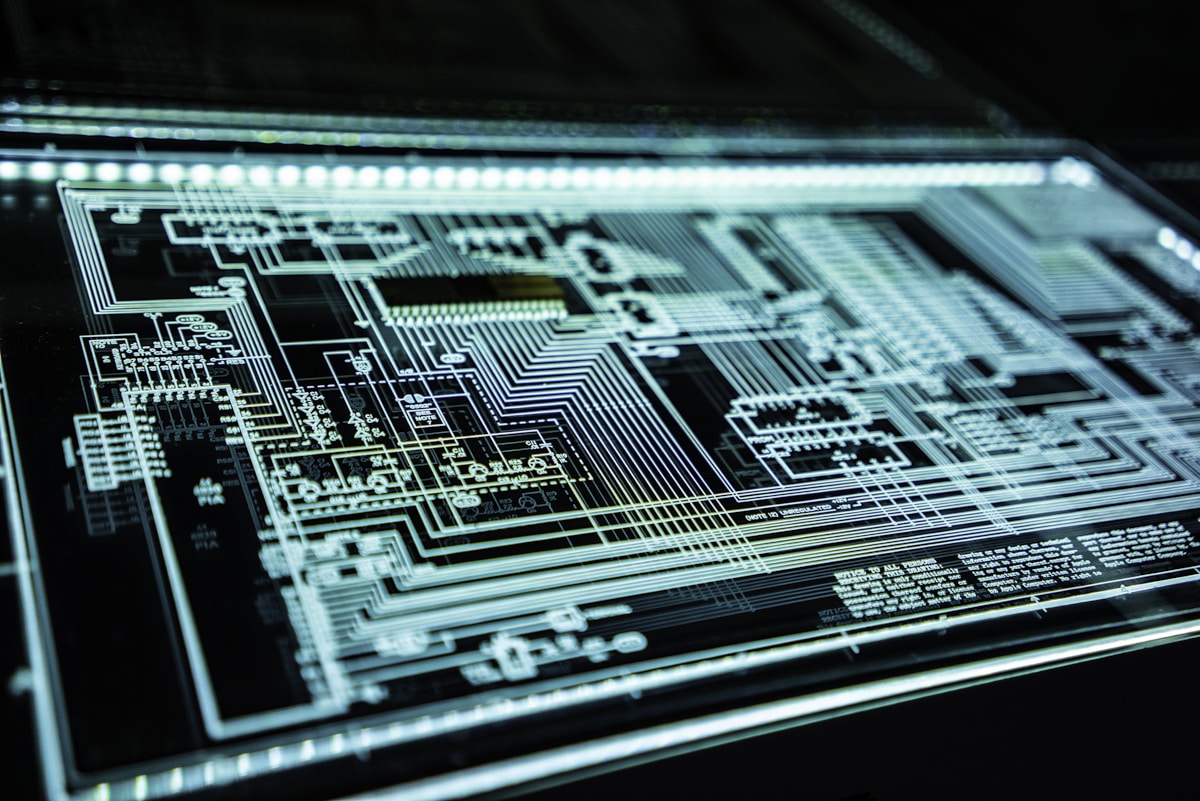

In the contemporary semiconductor landscape, the transition from architectural specification to physical silicon is a complex engineering process. This transition is governed by the RTL to GDSII design flow, a methodology that transforms hardware description languages into the geometric patterns required for lithography. As demand for high-performance computing and mobile efficiency scales, understanding this flow is essential for Advanced ASIC Design and Custom Silicon Implementation.

The term 'RTL' stands for Register Transfer Level, representing the functional behavior of the circuit, while 'GDSII' (Graphic Data System II) is the industry-standard database file format for the integrated circuit layout. The bridge between these two points involves a sequence of logical and physical design stages, each requiring precise validation to ensure the final chip meets its Power, Performance, and Area (PPA) targets.

Step 1: RTL Design and Functional Verification

The process begins with RTL coding using Hardware Description Languages (HDLs) such as Verilog, SystemVerilog, or VHDL. At this stage, engineers define the digital logic, registers, and data paths. For instance, in an AI accelerator, the RTL defines the systolic arrays and memory controllers responsible for tensor operations.

Functional verification follows coding. This phase involves simulation and formal verification to ensure the RTL behaves as intended. Verification engineers utilize Universal Verification Methodology (UVM) to identify bugs before they propagate into the physical design stages. A failure to catch a logic error at this stage can result in a costly re-spin of the silicon.

Step 2: Logic Synthesis and SDC Generation

Once the RTL is verified, it is translated into a gate-level netlist. This logic synthesis process uses Electronic Design Automation (EDA) tools to map code to specific logic gates provided by a semiconductor foundry’s Standard Cell Library. These libraries are part of the Process Design Kit (PDK), which contains the physical and electrical characteristics of the target manufacturing node, such as 7nm or 5nm.

A critical output of this stage is the Synopsys Design Constraints (SDC) file. The SDC defines timing requirements, clock frequencies, and input/output delays. For example, if a chip is designed to run at a clock frequency of 2.5 GHz, the synthesis tool must optimize logic paths to meet the 400-picosecond clock period. If the logic is too complex for the target frequency, the tool reports timing violations that must be addressed through RTL optimization or synthesis techniques.

Step 3: Floorplanning and Power Planning

The transition to physical design begins with floorplanning. This step involves defining the die area and the placement of functional blocks, known as macros (such as SRAMs, PLLs, and I/O pads). Effective floorplanning minimizes congestion and ensures efficient signal paths. In a system-on-chip (SoC), the floorplan must isolate analog components from high-speed digital logic to prevent interference.

Concurrent with floorplanning is power planning. Engineers design the Power Delivery Network (PDN), creating a grid of metal layers that distribute voltage across the die. A robust power grid is necessary to prevent IR drop, which can lead to timing failures or functional instability.

Step 4: Placement and Optimization

With macros fixed, the EDA tool positions standard cells within the floorplan. Placement tools are timing-driven, prioritizing the proximity of cells on critical timing paths to minimize total wire length. During placement, the tool performs optimizations such as gate resizing and buffer insertion to maintain signal integrity across long metal traces.

Step 5: Clock Tree Synthesis (CTS)

Clock Tree Synthesis (CTS) creates a balanced distribution network to ensure the clock signal reaches every flip-flop synchronously. CTS aims to minimize clock skew and clock latency. In high-performance designs, engineers implement techniques such as clock gating to reduce power consumption by disabling the clock for inactive portions of the circuit.

Step 6: Routing

Routing connects the cells and clock tree using available metal layers. This is divided into Global Routing and Detail Routing. Global routing allocates general signal paths, while detail routing defines specific metal traces and vias according to the foundry's Design Rule Manual (DRM). Routing in advanced nodes involves navigating complex Design Rule Checks (DRC) and mitigating effects such as crosstalk through spacing or shielding.

Step 7: Physical Verification and Sign-off

The final phase is physical verification and sign-off. The design undergoes several checks: Design Rule Check (DRC) for manufacturing constraints, Layout Vs Schematic (LVS) to match the layout to the netlist, and Static Timing Analysis (STA) to ensure timing requirements are met across process, voltage, and temperature variations. Once all checks pass, the design is exported as a GDSII file for photomask creation and fabrication.

Conclusion and Future Trends

The RTL to GDSII design flow requires a balance of automation and engineering expertise. As manufacturing processes move toward 3nm and 2nm nodes, the industry is incorporating Artificial Intelligence and Machine Learning (AI/ML) to optimize these steps. AI-driven EDA tools can explore a vast number of design iterations more efficiently than manual methods. Mastering this flow is a strategic requirement for organizations developing next-generation custom silicon.

Sources

- Weste, N. H., & Harris, D. CMOS VLSI Design: A Circuits and Systems Perspective.

- Synopsys, Inc. Digital Design and Implementation Flow Documentation.

- Cadence Design Systems. Advanced Physical Implementation Methodologies.

- IEEE Xplore Digital Library. Trends in Automated ASIC Design Flows.

This article was AI-assisted and reviewed for factual integrity.

Photo by Unsplash on Unsplash

Post a Comment