RISC-V vs ARM Architecture Performance Comparison: The Battle for the Future of Silicon

RISC-V vs ARM Architecture Performance Comparison: The Battle for the Future of Silicon

Senior Technology Analyst | Covering Enterprise IT, AI & Emerging Trends

The Great Architectural Shift: ARM vs. RISC-V

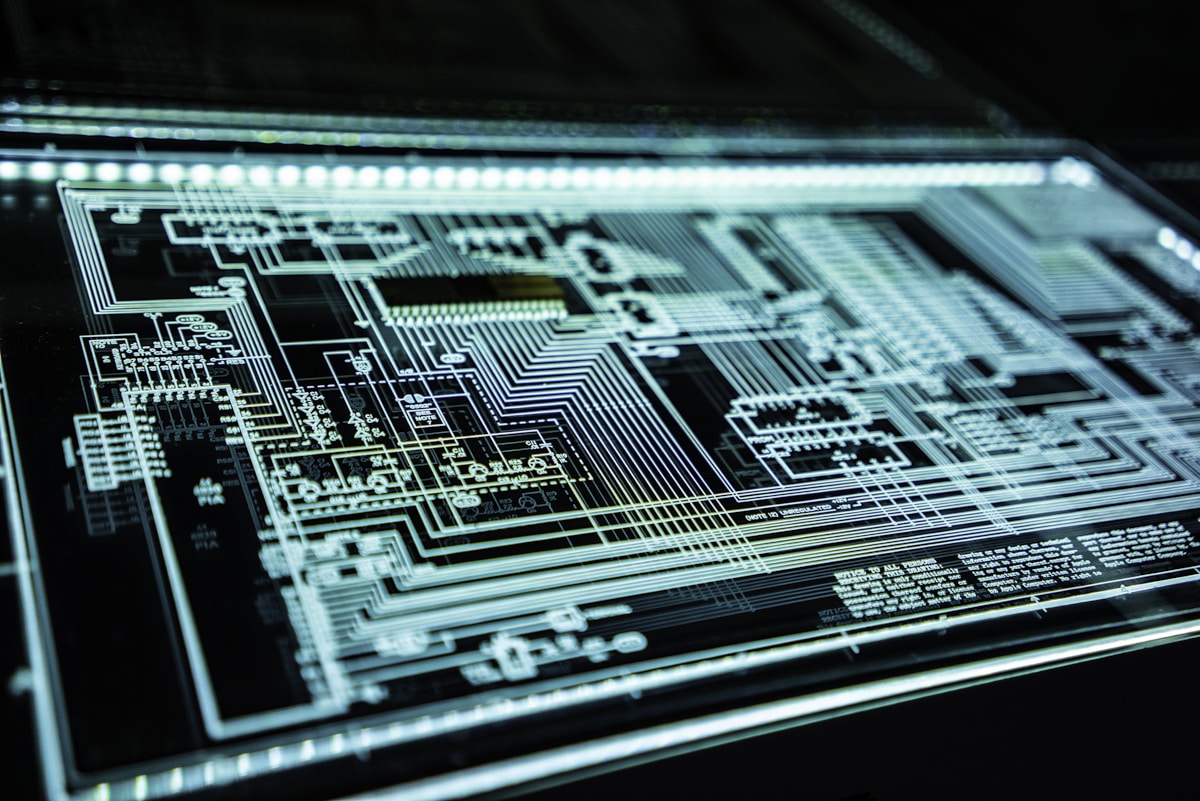

For over three decades, the semiconductor landscape has been dominated by established architectures. In the mobile and embedded sectors, ARM (Advanced RISC Machines) provides the foundational architecture for a vast range of devices, from smartphones to industrial sensors. However, the emergence of RISC-V, an open-standard Instruction Set Architecture (ISA), is providing an alternative to ARM’s proprietary model. This comparison examines the performance and structural differences between the two architectures.

The Fundamental Divergence: Proprietary vs. Open-Standard

ARM is a proprietary architecture. Companies license the ISA or specific core designs from ARM Holdings. This model provides a standardized, verified ecosystem but limits the ability of licensees to modify the base instruction set. Adding custom hardware accelerators typically requires specific licensing agreements and architectural permissions.

RISC-V is an open-standard ISA maintained by RISC-V International. It is a specification rather than a physical processor design. This allows vendors such as SiFive, Ventana, and Esperanto to develop custom cores that remain compatible with the broader ecosystem while incorporating proprietary extensions. This modularity allows designers to include only the necessary instructions for a specific task, potentially reducing silicon area and power consumption.

Performance Benchmarking: Throughput and IPC

ARM currently leads in the high-end consumer market. The ARM Neoverse and Cortex-X series feature high Instructions Per Cycle (IPC) and clock speeds resulting from extensive microarchitectural development. In standardized benchmarks, high-end ARM cores demonstrate mature branch prediction and out-of-order execution capabilities.

RISC-V implementations are advancing into high-performance computing. The Ventana Veyron V1, for instance, is designed for data center applications and utilizes a chiplet-based design for scalability. In multi-threaded workloads, the modularity of RISC-V allows for high core density, which can provide competitive aggregate performance per watt in server environments.

Power Efficiency and Thermal Envelopes

ARM utilizes the 'big.LITTLE' architecture to balance performance and power efficiency, making it a standard for battery-powered devices. RISC-V offers a streamlined base ISA; the RV32I implementation contains fewer than 50 instructions. This simplicity enables the design of efficient logic gates for ultra-low-power applications. In embedded applications, custom RISC-V cores have demonstrated reduced power consumption compared to standard general-purpose cores by eliminating unnecessary architectural overhead.

The Customization Advantage: Modular Instruction Sets

ARM’s ISA is a fixed standard. While it includes extensions like the Scalable Vector Extension (SVE), these are defined by the architecture's specifications. RISC-V is modular, consisting of a base integer ISA and various standard extensions (e.g., Vector, Floating-Point, Atomic). The RISC-V Vector Extension (RVV) allows designers to adjust vector lengths based on the hardware requirements. This enables specialized chips for AI inference to achieve significant performance gains over general-purpose processors by optimizing hardware for specific data types.

Ecosystem Maturity and Software Support

ARM possesses a mature ecosystem with highly optimized compilers, operating systems, and middleware. This software maturity ensures that applications are finely tuned for ARM’s pipeline stages. RISC-V is expanding its software support; major Linux distributions have been ported, and Google has designated RISC-V as a tier-1 platform for Android. While the RISC-V ecosystem is growing, high-end server and desktop applications still require further compiler optimization to match the maturity of established architectures.

Case Studies

- Aerospace: NASA selected SiFive to provide RISC-V cores for its High-Performance Spaceflight Computing (HPSC) processor, citing the need for an architecture that allows for specific fault-tolerant customizations.

- Wearables: Some manufacturers utilize RISC-V for low-power co-processors to handle background tasks, while maintaining ARM for the primary application processor to ensure compatibility with existing mobile operating systems.

Conclusion

The choice between ARM and RISC-V depends on the application. ARM remains the primary choice for the general-purpose consumer market due to its proven performance and extensive software ecosystem. RISC-V offers significant advantages in flexibility and customization for specialized workloads, data center accelerators, and low-power IoT devices. As the industry moves toward domain-specific computing, RISC-V provides a modular alternative to traditional proprietary architectures.

This article was AI-assisted and reviewed for factual integrity.

Photo by Unsplash on Unsplash

Post a Comment