RISC-V vs ARM Performance Benchmarks: The Battle for Semiconductor Supremacy

RISC-V vs ARM Performance Benchmarks: The Battle for Semiconductor Supremacy

Senior Technology Analyst | Covering Enterprise IT, AI & Emerging Trends

The Shifting Paradigm of Instruction Set Architectures

The semiconductor landscape has historically been defined by a duopoly of architectures: x86 for high-performance computing and ARM for mobile and embedded systems. However, the emergence of RISC-V has introduced a new variable. As an open-source Instruction Set Architecture (ISA), RISC-V allows designers to develop custom silicon without the licensing constraints or royalties associated with proprietary architectures. For senior architects and decision-makers, the evaluation now rests on how RISC-V and ARM performance benchmarks compare in production environments.

An ISA serves as the specification; actual performance is a product of the microarchitecture—the specific implementation in silicon. While ARM has refined its microarchitectures over several decades, including the Cortex and Neoverse series, RISC-V implementations are advancing through rapid iteration and collaborative development within the open-source ecosystem.

Core-to-Core Comparisons: SiFive P550 vs. ARM Cortex-A78

A primary industry benchmark involves the SiFive Performance P550, a high-end RISC-V core, compared against the ARM Cortex-A78. In SPECint2006 testing, the P550 demonstrated performance density comparable to the Cortex-A78. While the Cortex-A78 remains a standard in the mobile market, the P550 achieved competitive throughput with a reduced silicon footprint.

Data indicates that the P550 offers approximately 8.65/GHz in SPECint2006. This benchmark indicates that RISC-V is capable of handling complex, out-of-order execution tasks previously reserved for proprietary designs. ARM maintains a lead in peak single-thread performance in specific configurations due to mature branch prediction units and pipeline depth.

Efficiency and Power Scaling in Embedded Systems

In the embedded space, the comparison focuses on performance-per-watt. ARM’s Cortex-M series is a long-standing standard for IoT devices. However, benchmarks of the RISC-V Western Digital SweRV cores show that for specific storage and networking tasks, RISC-V can match or exceed ARM’s equivalents in cycles per instruction (CPI) and power efficiency.

The Western Digital SweRV EH1 benchmarks at 4.9 CoreMark/MHz, while the ARM Cortex-M7 typically reaches approximately 5.0 CoreMark/MHz. Beyond raw numbers, the RISC-V core offers extensibility. Designers can add custom instructions to the RISC-V ISA to accelerate specific workloads, such as bit manipulation or cryptographic hashing. This customization can result in performance gains for specific applications that are difficult to achieve with a fixed ISA.

Vector Extensions and High-Performance Computing (HPC)

The competition is extending into the data center and AI acceleration. ARM’s Scalable Vector Extension (SVE) is utilized in high-performance computing environments, such as the Fugaku supercomputer, allowing for flexible vector lengths for parallel workloads.

The RISC-V Vector (RVV) extension has also matured. Benchmarks from the Alibaba T-Head XuanTie C910 demonstrate that RISC-V can manage heavy computational loads. In AI inference tasks, the C910 showed that the open nature of the ISA allows engineers to optimize data paths between memory and vector units. While ARM currently leads the server market via implementations like Graviton and Ampere Altra, RVV implementations demonstrate that RISC-V is architecturally capable of high throughput in floating-point operations.

Software Ecosystem Maturity

A processor's performance is dependent on the software stack and compiler optimization. ARM benefits from a mature ecosystem where compilers such as GCC and LLVM have been tuned over decades for ARM silicon.

RISC-V software optimization is in a growth phase. In some benchmarks, RISC-V hardware performance is limited by compiler instruction scheduling rather than architectural flaws. This gap is narrowing as major contributions from the Rise Project and other industry collaborators improve the toolchains. Recent benchmarks show that as toolchains mature, the performance delta between similarly specified ARM and RISC-V hardware continues to decrease.

Customization and Domain-Specific Architectures

The technical advantage of RISC-V often lies in domain-specific acceleration. Because ARM is a proprietary, general-purpose ISA, users are generally restricted to the provided instruction set. In contrast, the open-source nature of RISC-V allows for the creation of Domain Specific Architectures (DSAs).

For example, a company specializing in image processing can add custom RISC-V instructions for pixel manipulation. In comparisons between standard ARM cores and customized RISC-V cores for image filtering tasks, the RISC-V core can achieve higher efficiency by reducing the cycles required for specialized mathematical operations. This ability to tailor hardware to specific software requirements is a primary driver of RISC-V adoption.

Conclusion

Current benchmarks indicate that while ARM maintains a lead in absolute performance for high-end mobile and server applications, RISC-V has achieved parity in the embedded and mid-range segments. The gap in high-performance computing is narrowing as the ecosystem evolves. For organizations, the choice between ARM and RISC-V involves a trade-off between the established maturity of ARM and the optimization potential of RISC-V.

This article was AI-assisted and reviewed for factual integrity.

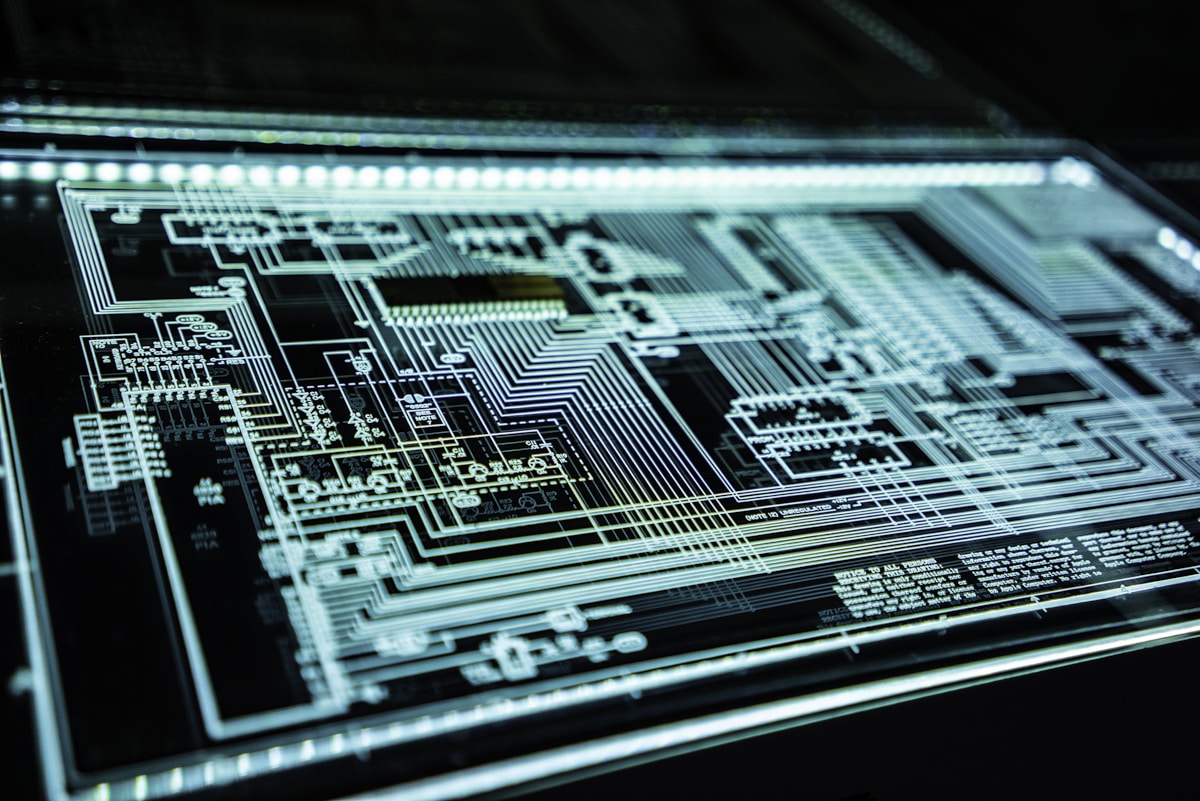

Photo by Unsplash on Unsplash

Post a Comment