The Lattice Trap: CRYSTALS-Kyber vs. FrodoKEM Latency in FPGA-Based Edge Architectures

The Lattice Trap: CRYSTALS-Kyber vs. FrodoKEM Latency in FPGA-Based Edge Architectures

Senior Technology Analyst | Covering Enterprise IT, Hardware & Emerging Trends

The Post-Quantum Reality Check: Edge Encryption

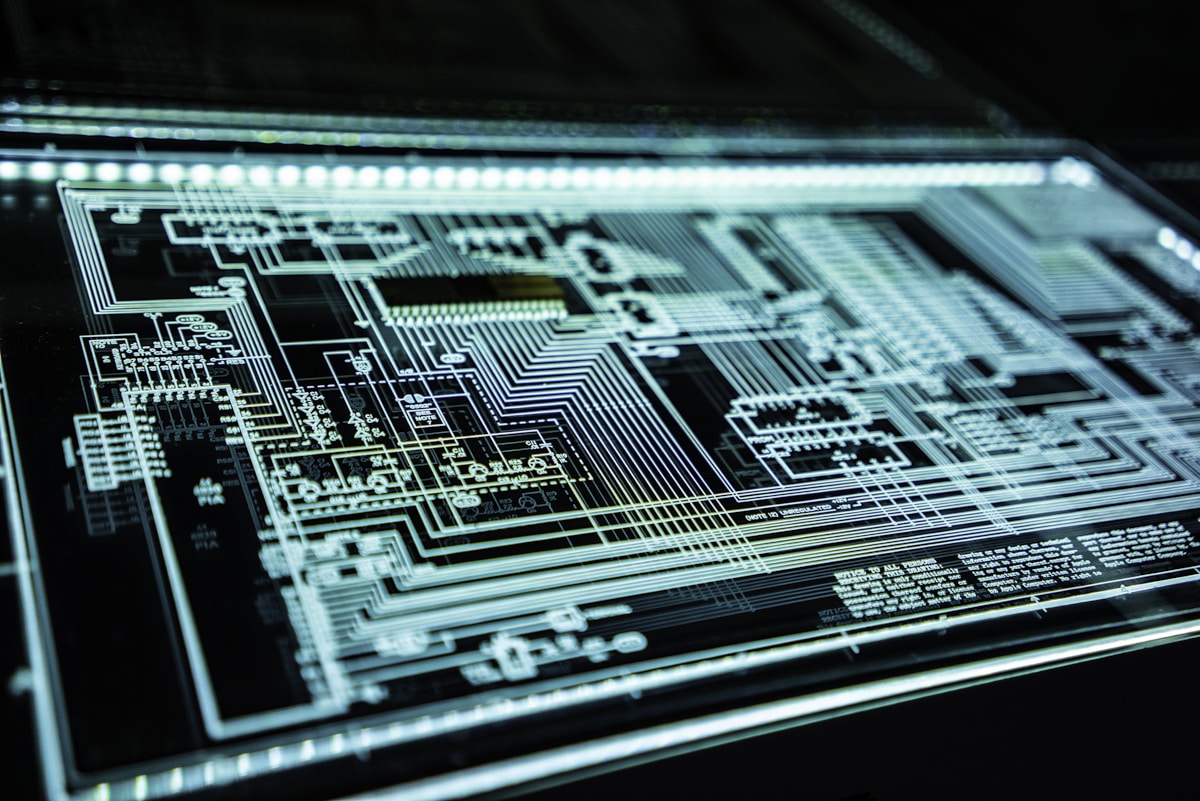

The NIST standardization process for Post-Quantum Cryptography (PQC) involves significant challenges regarding silicon-level implementation. PQC migration requires careful consideration of gate count and clock cycles required to execute lattice-based primitives on resource-constrained edge FPGAs.

The Latency Divide: CRYSTALS-Kyber vs. FrodoKEM

When architects evaluate CRYSTALS-Kyber (ML-KEM) against FrodoKEM, they are comparing different security philosophies. Kyber relies on the Module Learning With Errors (MLWE) problem, offering structured lattices that allow for compact implementations. FrodoKEM targets the plain Learning With Errors (LWE) problem, providing a more conservative security profile with higher resource requirements.

FPGA Implementation Metrics

- CRYSTALS-Kyber (ML-KEM-768): Optimized for DSP-heavy architectures. Latency for key encapsulation depends on the implementation of NTT (Number Theoretic Transform) cores.

- FrodoKEM-640: The memory footprint is significant. Without substantial BRAM allocation, FrodoKEM latency is impacted by matrix-vector multiplications that lack the algebraic shortcuts available to Kyber.

For those navigating Post-Quantum Cryptography (PQC) migration strategies for lattice-based NIST standard implementations, the choice depends on device constraints. FrodoKEM requires higher memory and data movement compared to Kyber.

Hardware Bottlenecks in Edge Deployments

A primary challenge is side-channel resistance. Implementing Kyber on an FPGA requires handling NTT units to mitigate power analysis attacks. Hardening these implementations against DPA (Differential Power Analysis) introduces latency overhead.

Key Architectural Considerations

- NTT Acceleration: Kyber's performance relies on efficient NTT hardware cores. Insufficient DSP slices may force serial implementations, impacting latency.

- Memory Bottlenecks: FrodoKEM’s matrix sizes require significant on-chip memory. In edge devices with limited block RAM, off-chip memory access may impact system responsiveness during the handshake phase.

- Throughput vs. Latency: In edge scenarios, time-to-first-byte is a critical metric. Kyber’s structural efficiency is a factor for real-time industrial IoT or automotive sensor fusion.

The Strategic Verdict

CRYSTALS-Kyber is widely utilized for edge hardware, while FrodoKEM is often reserved for high-resource backend gateways. There is an increasing availability of IP cores optimized for Kyber on SoC-FPGAs.

Hybrid-mode implementations—encapsulating current ECC keys within a Kyber wrapper—are being considered for compliance. Hardware roadmaps should account for the memory and DSP requirements of ML-KEM to ensure compatibility with emerging regulatory frameworks.

Post a Comment