The GPU Trust Gap: Verifying Hardware-Level Availability in zk-Proof DePINs

The GPU Trust Gap: Verifying Hardware-Level Availability in zk-Proof DePINs

Senior Technology Analyst | Covering Enterprise IT, Hardware & Emerging Trends

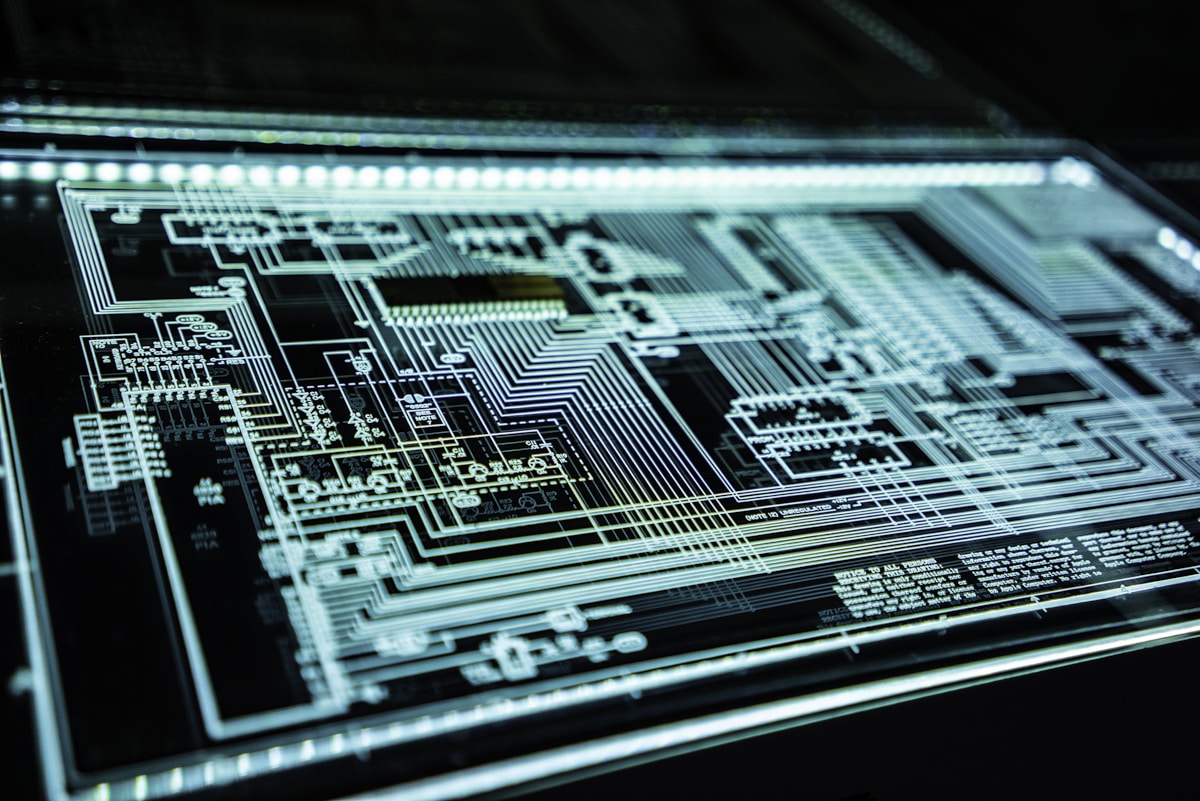

The Reality of Virtualized GPU Verification

If you rely solely on throughput reported by a remote node in a decentralized compute network, you face significant security risks. The industry is increasingly recognizing that software-level telemetry can be unreliable in permissionless environments. When a node claims to have specific hardware available for inference, it is possible for a malicious actor to spoof identifiers or emulate driver stacks to misrepresent the underlying hardware. If your architectural implementation of proof-of-physical-work (PoPW) consensus for decentralized edge-compute GPU clusters does not account for hardware-level verification, the network remains vulnerable to hardware spoofing.

The Anatomy of Hardware Verification

Verifying hardware in a zero-trust environment requires shifting the burden of proof from the software layer to the silicon itself. We are looking for cryptographic attestation of physical state. To achieve this, developers are exploring the use of Trusted Execution Environments (TEE) and hardware-level analysis.

The Core Verification Stack

- Intel SGX/TDX & AMD SEV-SNP: Utilizing memory encryption to isolate the verification agent from the host OS.

- PCIe TLP (Transaction Layer Packet) Analysis: Monitoring physical bus traffic to verify data interaction with GPU memory controllers.

- Zero-Knowledge Proofs (ZKP) of Compute: Generating proofs (via protocols like Halo2 or Plonky3) to verify that specific GPU architectures performed matrix multiplication.

- Thermal/Power Side-Channels: Using BMC (Baseboard Management Controller) data to correlate power draw with reported GPU utilization.

The Mechanics of Verification

The challenge in zk-proof DePIN architectures is proving that the GPU is actively dedicated to the task. We must implement Proof-of-Computation (PoC) cycles that are hardware-specific. By injecting micro-benchmarks that rely on specific core architectures, we can create a 'silicon fingerprint.' If the latency or instruction set execution deviates from the expected profile of the declared hardware, the node may be flagged.

Implementation Strategy

- Attestation Phase: The node provides a signed report from the hardware’s Root of Trust (RoT), confirming the serial number and firmware version.

- Challenge Phase: The network issues a non-deterministic, hardware-bound instruction set that is computationally expensive to emulate but efficient to execute on native silicon.

- Verification Phase: The node submits a ZK-proof confirming the correct execution of the challenge, bound to the hardware's unique ID.

The Latency-Security Tradeoff

Rigorous verification introduces latency. Every millisecond spent generating a ZK-proof is a millisecond the GPU is not generating revenue. Architects must balance 'Proof Frequency.' Continuous verification is technically ideal but can be economically inefficient. Instead, we are seeing the rise of Probabilistic Verification, where nodes are subjected to random 'spot-check' audits. If a node fails to provide a valid hardware attestation within a randomized window, the deposit may be subject to slashing. This creates an economic disincentive for spoofing.

The Future of Decentralized Compute

The industry is moving toward a standardized Hardware Attestation Layer. Projects that implement silicon-level verification are better positioned to provide enterprise-grade performance guarantees. The era of 'trust-me' decentralized cloud is shifting toward an era of 'verify-the-silicon.' Architects should prioritize these verification standards to ensure long-term network viability.

Post a Comment